By David L. Weaver

"OpenSPARC Internals: OpenSPARC T1 and T2 Chip Multithreaded (CMT) Throughput Computing" offers an creation to the open-source OpenSPARC T1 and T2 microprocessors. OpenSPARC T1 and T2 are the 1st and in simple terms open-source CMT (Chip Multi-Threaded) microprocessors and primary and in simple terms open-source 64-bit microprocessors in lifestyles. an entire T1 layout contains eight cores (32 threads), whereas T2 is eight cores (64 threads). This booklet comprises an outline of ways OpenSPARC could be positioned to educational or commerical use, developing improvement atmosphere, reconfiguring the deisgns to differing numbers of threads or cores, synthesizing OpenSPARC T1 into FPGA strategies, configuring/using OpenSPARC simulation software program, compiling software program for an OpenSPARC aim processor, and a few dives into the OpenSPARC resource code itself. (this ebook is usually on hand in PDF softcopy from the OpenSPARC website, http://OpenSPARC.net)

Read Online or Download OpenSPARC Internals PDF

Best computers & technology books

Booklet via

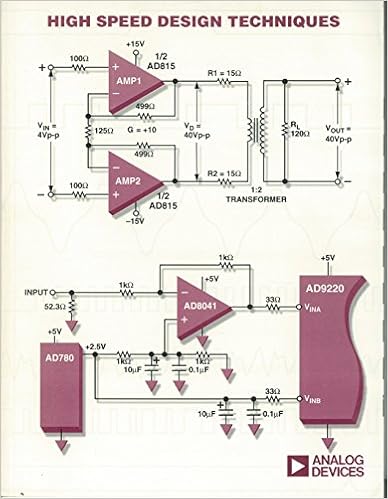

High-Speed Design Techniques (Seminar Series)

Booklet by way of Walt Kester

Imagining the Internet: Personalities, Predictions, Perspectives

Within the early Nineteen Nineties, humans estimated the dying of privateness, an finish to the present thought of "property," a paperless society, 500 channels of high-definition interactive tv, international peace, and the extinction of the human race after a takeover engineered by means of clever machines. Imagining the web zeroes in on predictions in regards to the Internet's destiny and revisits previous predictions--and how they grew to become out--to placed that imagined destiny in viewpoint.

Fundamentals of Power System Protection

Strength method is a hugely advanced dynamic entity. One malfunction or a clumsy set relay can jeopardize the total grid. strength approach defense as a subject matter bargains the entire components of intrigue, drama, and suspense whereas dealing with fault stipulations in genuine lifestyles.

Extra resources for OpenSPARC Internals

Sample text

Some specifics are left implementation-dependent. 3 Privileged Software UltraSPARC Architecture does not assume that all implementations must execute identical privileged software (operating systems) or hyperprivileged software (hypervisors). Thus, certain traits that are visible to privileged software may be tailored to the requirements of the system. 2 Processor Architecture An UltraSPARC Architecture processor—therefore an OpenSPARC processor—logically consists of an integer unit (IU) and a floating-point unit (FPU), each with its own registers.

OpenSPARC T2 supports an unsupported_page_size trap when an illegal page size is programmed into TSB registers or attempted to be loaded into the TLB. OpenSPARC T1 forces an illegal page size being programmed into TSB registers to be 256 Mbytes and generates a data_access_exception trap when a page with an illegal size is loaded into the TLB. • OpenSPARC T2 adds a demap real operation, which demaps all pages with r = 1 from the TLB. 40 Chapter 4 OpenSPARC T1 and T2 Processor Implementations • OpenSPARC T2 supports an I-TLB probe ASI.

Note that parking is similar to OpenSPARC T1’s idle state. OpenSPARC T2 does support an equivalent to the halt state, which on OpenSPARC T1 is entered by writing to HPR 1E16. However, OpenSPARC T2 does not support OpenSPARC T1’s STRAND_STS_REG ASR, which holds the strand state. Halted state is not software-visible on OpenSPARC T2. • OpenSPARC T2 does not support the INT_VEC_DIS register (which allows any OpenSPARC T1 strand to generate an interrupt, reset, idle, or resume message to any strand).